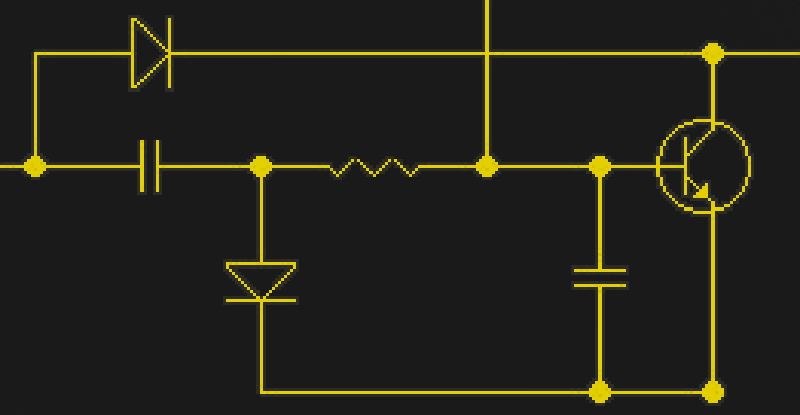

The Schmitt inverter is developed to operate within certain boundaries. This helps to avoid the errors that is related to the noise in the input signals. It can be implemented on several devices, however most commonly on the operational amplifier. Inverter NOT Circuit Schmitt InverterĪ Schmitt trigger is a circuit which generates an output waveform of a square wave of a particular duty cycle. This works same as the other inverter circuits designs it inverts the given input signal. The circuit of a practical inverter NOT circuit is made up of diodes, resistors and bipolar junction transistors. These states HIGH and LOW corresponds to logical 1 or 0 respectively. Usually digital electronic circuits operate in constant levels of 5V, 3V for “HIGH” state and 0V for LOW state. The bipolar junction transistor must be saturated “HIGH” (“ON”) for a complemented output “LOW” (“OFF”). We can develop a simple two input circuit as shown in the diagram below. It is built using resistors considering them as the input network. The design is based on the class of digital circuit build which is also known as resistor transistor logic. We can easily design and build a NOT gate using Bipolar Junction Transistors. Though this design manufacturing costs are higher than the others it consumes less power and has a high processing speed. There are methods to design NOT gate inverters using two inverting transistors which uses Complementary Metal Oxide Semiconductor configuration. This can be fabricated at lower manufacturing costs compared to others. We can easily design and build a NOT gate using a single N-type Metal Oxide Semiconductor transistor using a P-type Metal Oxide Semiconductor transistor by coupling it with a resistor.

Then if the input voltage at the point A is HIGH the output voltage at the point Q will be LOW. This produces a output voltage of HIGH at point “Q”. When the base of the transistor is LOW, the transistor starts to stop the current flowing through the resistor connected to the collector. This produces a voltage drop across the Resistor connected to the collector and connects the output point at “Q” to ground making a zero-voltage output at point “Q”. When the base of the transistor circuit is HIGH, the transistor starts to conduct and the current in the collector starts to flow. We can design a simple NOT gate inverter circuit using a single stage transistor switching circuit as shown in the diagram below. Let’s label A as input and the Q is the output. Not gate truth tableįollowing is the truth table for NOT gate. This symbol is not limited to the NOT gate, we can apply these for any other digital circuits, and it represents the negation of the corresponding signal. This is also called as the Bubble symbol, and this can also placed at the beginning of the diagram to indicate an active – LOW input. The “O” mark which is at the end of the Traditional and IEC symbol of the gate denotes the complementation of the input signal.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed